评测 | 国产FPGA使用体验

周末闲谈,今天我来评测一下国产FPGA,这几个月在做比赛,用的正是我们国产FPGA紫光同创Pango PGT180H,这两年FPGA也是越来越火,应用越来越多,不知道能不能搭上人工智能的这趟顺风车,大红大紫呢。Xilinx和Altera(现Intel)两家加起来占了90%的市场份额,毕竟行业在国外起步比我们早太多了。既然现在也有了国产FPGA了,可能没有上市发售并没有多少人知道,我呢,参加比赛有幸使用了一下由深圳市紫光同创电子有限公司开发的FPGA,那么用户体验如何呢,今天我们就来聊聊这款Pango PGT180H。

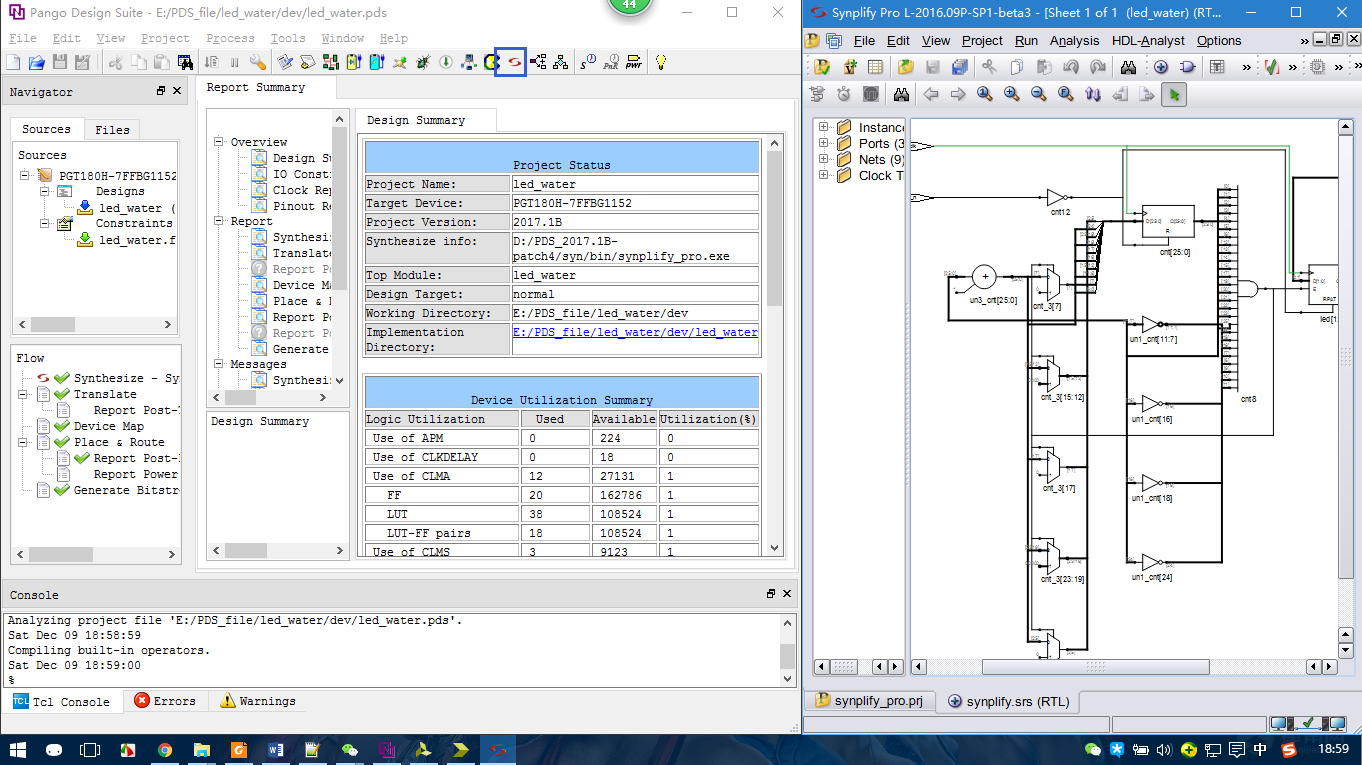

首先,综合工具。都说了是国产,那么芯片肯定也是国产的喽。肯定使用自家的综合工具。紫光同创出的综合工具是Pango Design Suite,简称PDS。我不由的想和业界标杆做比较了。如下图。

这是PDS 2017.1的界面

这是ISE14.7的界面

这是Vivado 2017.3的界面

这是Quartus II 13.0的界面

恩,相信已经有朋友看出来了,PDS这个界面还真和ISE有点神似,不过相似没关系,看着还算简洁,而且PDS的软件安装包只有三百多兆,比起其他几款都小了很多,可能是紫光的产品还比较少吧,据我所知,目前紫光只有两款FPGA,X家和A家多的都数不过来了。PDS在编译速度上还是比较慢的,我用我的i3低功耗笔记本实测几款主流综合工具,对于一个流水灯来说。ISE14.7和QuartusII13.0可能不到一分钟就编译完成,Vivado可能是由于内部算法的不同,会有2-3分钟的时间,PDS我没有掐表,目测五分钟是有了。不过对于工程量大的设计,PDS的速度也没有很明显的降下来,我们比赛做的项目最后的大工程,我电脑用ISE14.7跑了有二十分钟吧,PDS用的时间少了一点。综合来说PDS在编译速度上基本与ISE14.7持平,小工程ISE14.7完胜,大工程PDS略占便宜。毕竟ISE已经停更了么。当然在人性化设计和美观上评价,我认为ISE还是好,也可能是我用习惯了吧。

对于软件还有很多地方需要说说,比如我们要看自己写的代码的原理图的话,ISE上直接点击Synthesize-XST下的View RTL Schematic便可直接打开,那么PDS呢,需要重新打开一个新的界面(貌似是一个软件),然后才能查看。

引脚分配文件的话,PDS后缀为fdc,打开文件里面是这样的。

ISE是这样的,恩还是ISE的好修改,好看。

IP调用界面的话,恩都差不多,都不怎么好看。

但是紫光的IP使用的话,我是必须要吐槽一下了,首先来说说PLL IP Core的调用,我对于X家和A家的软件的话,我使用的时候感觉很便捷,填写输入时钟,直接填写输出时钟,然后直接输出,至于相位偏移和占空比也是可以直接调的。PDS来了。

上图中的1部分是输入时钟的,2部分是输出时钟的,那么下面第3部分就是用2部分倍频的时钟再分频出来,输出你要的时钟,也就是说,比如你需要75Mhz,那么保证是整数分频的话,你需要首先最少需要倍频到150Mhz然后对150Mhz的时钟进行3分频,最后才是输出你需要的时钟,那如果我需要一个99Mhz的时钟呢,对不起支持不了,当然我们实际使用的过程中也不需要那么奇葩的时钟了。

接下来时RAM IP Core了,PGT180H的资源很多,芯片里面的存储是一块一块的,一块是18kbit,一共有526个,这算是很大的容量了,你需要的多的时候,它会自动拼接。

但是里面还有限制,比如下图

最多只能用这么多了,再多的话生成两块拼起来也可以,不过一般情况也不会一次用这么多,除非一样显示很大的图片,对,我显示了。最后就是PDS自带的编辑器了,说实话很不好用,虽然ISE也一样很不好用,但是至少软件支持和第三方编辑器级联,但是PDS不支持,所以我这也有一点小建议了,就是希望PDS后面的版本可以支持第三方编辑器级联,记住这是我建议的,后面如果紫光真的支持了,那肯定是听了我的建议。至于软件其他的一些功能使用,我使用时间也不长,就暂且不谈。

吐了这么多软件的嘈,我们的主角还没登场呢,那就是Pango PGT180H,我们先来看一下这款板子样子。

从上图中可以看出,芯片还是比较大的,这块芯片采用的40nm工艺制成,28nm的zynq 7010比较了一下了,差不多是zynq的4倍,毕竟工艺不同,而且单说PL部分的资源PGT180H可以说可以虐zynq了,但是不要忘了zynq上还嵌入了双核arm呢。

l FPGA: PGT180H 约 180K 等效 4 输入 LUT, 3 个 HSST Quad, 每个 HSST Quad 支持

四个全双工收发 Channel

l 3 个 HSST Quad

Ø 1 路高速串行收发器(HSST)连接到 1x9 光模块, SGMII 接口, 速率 1.25Gbps

Ø 4 路高速串行收发器(HSST)连接到标准的 PCIe x 4 金手指,支持 PCIe Gen1/Gen2

Ø 4 路高速串行收发器(HSST)连接到 SMA 头上,可编程晶振提供参考时钟

l 2 个 16 位 4Gb 容量的 DDR3 芯片组成的 32 位宽的 DDR3 内存,速率达 1066Mbps

l HDMI 发送和接收,发送芯片为 ADV7511,接收芯片为 ADV7611, TYPE A 型 HDMI

座子

l 支持 RGMII 接口的 10/100/1000M 以太网 PHY

l USB 转 UART 接口, MINI B 型 USB 座子

l 用户及扩展 I/O

Ø 4 个 LED

Ø 4 个按键

Ø 2 个 4 位拨码开关

Ø 72 个扩展 I/O,连接到标准的 2 个 2 x 20 pin 的 2.54mm 间距双排针,双排针上有

5V 和 3.3V 电源和地,可供用户扩展子卡使用

l 2 个可插拔的带底座的有源晶振,一个连接到 FPGA 的 GCLK 引脚,另一个连接到 FPGA

的 PLL 引脚

l 配置模式

Ø 支持 JTAG 模式

Ø 支持 SPI Master 模式

Ø 支持 32 位 parallel slave 配置模式

l 电源供电:采用 12V 直流供电, 为内核供电的电源芯片可提供 6A 电流, 高速收发部分电

源采用低纹波的 LDO 单独供电

上面这是一些官方的参数了。可以看到,PGT180H的资源还是很丰富的。该有的都有,HDMI、千兆以太网、光模块、DDR3、PCIE、SMA我都没听过的都有,目测如果开开卖的话,肯定得几千。这么多高大上的外设,还是不能掩盖它的槽点。

首先第一个就是晶振,板子上有两个可插拔晶振四脚(人家早都集成到板子上了好不),一个是50Mhz用来pll的输入,一个用作33Mhz系统时钟,这和手册上说的完全相反,我们用户使用的时候,可就坑了,那33Mhz的系统时钟该如何是好,初步推测是手册写错了。不过我用的时候直接用50Mhz的那个引脚了,而且其实给我寄的开发板50Mhz那个晶振是坏的,搞得我还去电子大楼被大叔大妈们坑了一波,一个晶振管我要15,你敢想。

然后是拨码开关,板子上有8个拨码开关,是的八个,一个都用不了,它粘死了,拨都拨不动,我还不敢用力,只能不用了,据我所知,其他一些组也有这种情况。

吐槽了这么久,我也吐槽累了,心中只想说一句,此生不再用国产。

不过其实话说回来,我们这次使用这款FPGA确实在代码移植上遇到了一些问题,但是最后也都迎刃而解,而且代码移植过来完全适用,没有任何bug,而且PGT180H的资源非常丰富,IO口也有很多,在我们没有调试出HDMI的时候,买个20pin的VGA模块也能勉强用,外加摄像头模块也十分给力,官方的Pll虽然也有一些槽点,但是经过我实测发现,我写的分25Mhz分频,就是没人家Pll分出的25Mhz驱动摄像头稳定,还有一点我觉得比较好的是,PGT180H的RAM支持异步复位同步释放,还真有点意思,

同样的工程

这是两个同样的工程,1、3幅图为PGT180H的资源使用率,2、4是zynq7010 PL部分的资源使用率,结果很明显,PGT180H可以吊打zynq7010 PL部分资源了,即使是最后的大工程,我们除了RAM使用超过了50%以外,其他都超不过10%。而且PDS软件在综合上,对于大工程来说还是要比ISE快啊,所以最后还是对我们有些好处的。我们从开始构思到准备这个项目,已经有两个多月了,回想起来这两个多月也发生了很多事情,遇到了很多困难,但幸运的是最后都能慢慢化解,真是一路心酸带泪啊,结束后只是感谢自己一直没有放弃,坚持自己的选择。

总的来说,我对国产FPGA的感觉还是充满希望的,因为我看到我们国产在努力,国产在进步,这款FPGA算是高端系列了,我能用到的并不多,所以只能给一些浅薄的评价,不过我相信国产,我们也在进步,随着技术的积累我们一定会慢慢的缩小差距的。

声明: 刚开始抱着好玩的心态写这篇评测,没想到最后文章都传到紫光原厂了,才发表一天个人微信号上的阅读量达到了500+老实说,在使用过程中是有些嘈点和不习惯,但是也给了我们很多惊喜,现在将这篇文章发到我的专栏里,顺便推广下自己的订阅号: 硅农

文章被以下专栏收录